DC知识点总结

编写脚本用于处理综合报告信息

在分析综合报告的时候,用户往往只关注部分重要的的报告信息。而一次综合流程输出的报告数目比较多,在阅读和分析过程往往会令人无从下手,因此设计一个脚本文件,当用户在./report文件下执行脚本后,自动生成一个报告总结,汇总需要用户关注的报告信息。

Tcl脚本思路

伪代码的书写思路大致如下所示,具体的代码则需要更加细致的补充

1 | |

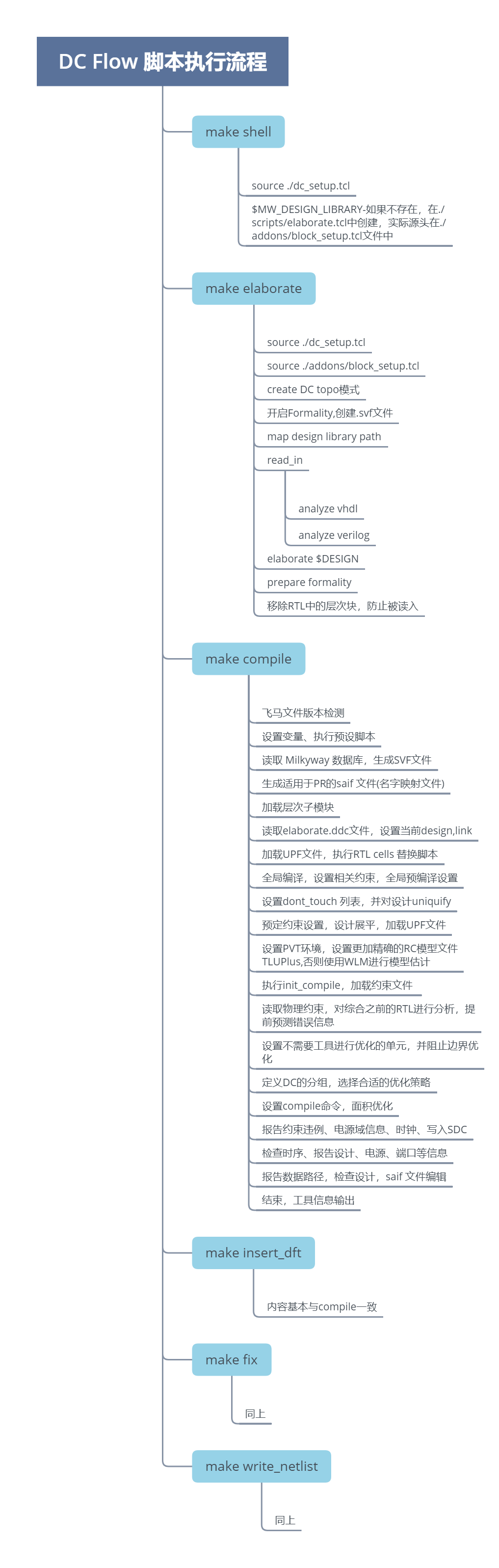

上述图片是实际项目过程中的命令执行流程,在实际的工作环境中,每一步骤都会处理上一步骤的环境配置,因此每一次都会加载上一次的信息,这是一个重复的过程,因此在脚本环境中,会出现重复读入输入,并利用同一个命令输出每一步骤的报告。

在设计中,实际的效率并不高,特别是当设计模块已经到达千万,甚至上亿门之后,综合要求更多的软件运行时间,如果某一步骤运行出错,会导致下一步骤无法运行,这对综合人员来说也是一种压力,特别是在后端进度实际就是为了给前端节省时间的情况之下。

在上图的内容中,综合过程可以概括为compiler+elaborate,之后的insert_dft 属于DFT工程师的设计内容在实际的过程中,综合工程师可能在了解原理的情况下进行dft的插入

DC优化设计方式:给指定功能提供最小、最快的逻辑实现。

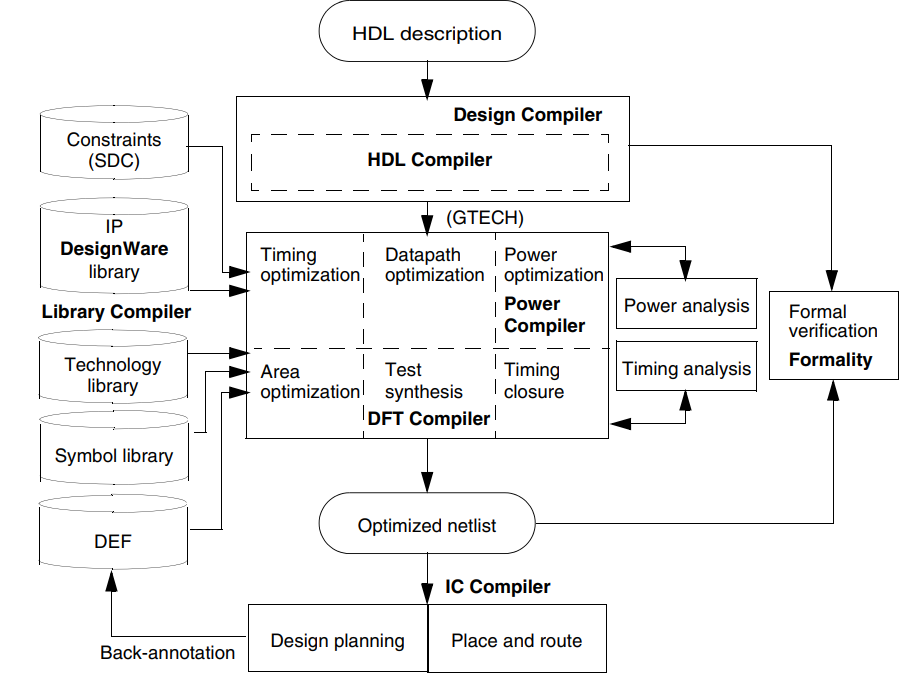

DC的过程:综合HDL,将其转换为optimized, technology-dependent, gate-level design. 支持flat 和 hierarchical design, 支持组合和时序设计,主要进行面积,时序,功耗优化。

DC工具简介

DC Expert keyword: Wire load Mode, WLM

DC Ultra keyword: concurrent(并发) advanced optimization,high performance design, Topographical technology-可以用来精确估计设计的物理信息

DC Graphical keyword: optimize MMMC design, reduce congestion, improve runtime in ICC, floorplan

DC Expert Feature

- 层次化编译(bottom-up or top-down)

- 全编译,增量编译

- 为复杂的 Flip-Flop 和latch 做时序优化

- 基于latch设计的时序补偿

- 时序分析

- 命令行及GUI

DC Ultra Feature(相比 DCE 增加的)

- 更快的运行时间

- 先进的算法优化

- 集成datapath partition and synthesis

- 先进时序分析

- 先进的延时优化算法

- 先进的

leakage power优化 - register retiming(工具通过在组合逻辑间移动register优化时序)

DC Ultra in Topographical technology

- 多电压多供电设计

- Concurrent MMMC优化,减少迭代次数提高,获得结果的时间效率

- 和ICC共享 Placement以及优化技术,使用更准确的数据处理,提高设计质量

DC Graphical Feature

- 优化MMMC design

- 减少Routing Congestion

- 提高area, timing与ICC的联系

- 提高在ICC中的运行时间与可布线性

- 创建和修改Floorplan (using Floorplan Exploration)

- Physical guidence technology,包含enhanced placement,提高QoR等能力

DC in Design Flow

DC术语

尽管下面术语有轻微的不同,在DC manual 中可以看作相等的含义。

Synthesis: 指为RTL生成 gate-level netlist的过程,过程包含read design 和 optimize design

Optimization: 是Synthesis中的一步操作,指完成(选择)满足设计约束的library cell 集合

Compile: 是Design Compiler 的过程,用来执行synthesis 和 optimization

Design

Design:实现逻辑功能的电路描述。

Logical-level Design: 使用 Boolen equation 实现

Gate-level Design: 使用 Interconnect cell 实现

Flat Design: 不包含子设计,只有一个结构层次,且只包含library celll

Hierarchical Design: 包含子设计,子设计也可以包含子设计,创建多个层次结构

Reference: 一个用来搭建更大电路的library component or design

Leaf cell: 只包含一个设计的unique instance

Port: 端口拥有方向,input, output, inout

DC支持的Flow类型

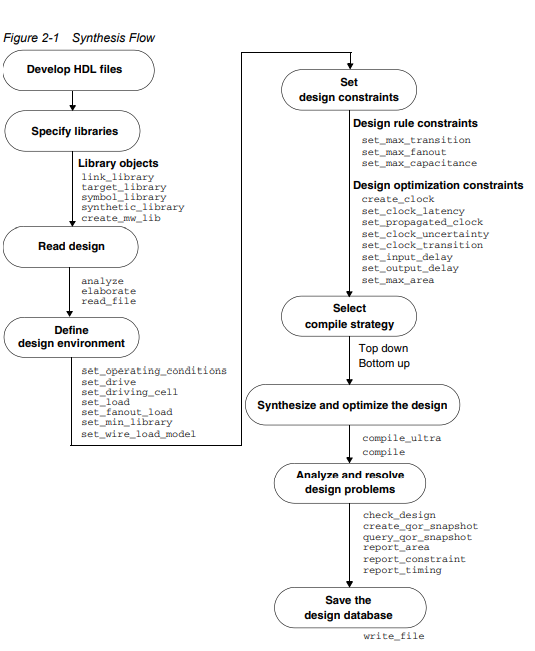

Full compile: DC map、optimize整个设计,产生一个gate-level netlist,并且如果设计中存在已经mapped cell也会被 unmapped,该Flow不会保护已经存在的netlist结构。

Incremental compile: DC 可以通过改善设计结构提高design QoR,它是在init compile的基础上进行mapping, 主要集中在未满足约束的area设计上,已经存在的netlist会被保护起来,mapping 优化只有在能够改善设计的基础上被采用

编译策略

Top-down: top-level design 和子设计共同编译.

Bottom-up: 子设计分开编译,从底层一直变异到top-level.

Mixed: 小模块使用Top-down,大模块使用Bottom-up.

Optimization

基于约束与变量进行优化,将设计转换成library cell,其理念是如果设计能够减少功耗且不增加其他设计模块的功耗,则可以采用该cell,完成优化

Design Compiler Mode

Wire Load Mode:线性负载模型,延时计算使用估计,精度较差

Topographical Mode:拓扑模型,延时计算精确性更高

Multimode: 多corner,多mode

UPF Mode: UPF低功耗

WLM:在默认情况下,dc_shell会启用WLM, 使用线性负载进行时序预估,此时compile 和compile_ultra都是在WLM下进行synthesis过程

Topographical: 需要命令dc_sell -topographical_mode启用,此时compile_ultra和compile_ulra -spg都工作在拓扑模式,且-spg工作在DC Graphical模式,会使用到后端Floorplan的物理信息。

Setup File

DC 从三个文件位置读取.synopsys_dc.setup文件

1 | |

Name Rules

一些制造厂可能会自己修改命令规则,比如将Design Ware中的cell 转换成U , 将 reset转换成RET等

用户也可以通过命令修改命名规则,define_name_rules 和 change_name可以用来改变port 和 net的名称

dc_shell执行的程序过程

1.创建log文件

2.读取.synopsys_dc.setup文件

3.Batch Mode下执行脚本文件

4.展示DC应用的信息

重定向标准输入输出

重定向命令可以分成三个命令:

1 | |

The Synthesis Flow

Using Multicore Technology

DC 支持使用多核技术完成程序运行任务,每个license支持 8 cores, 可以使用命令设置多核功能

1 | |

通过多核技术提高运行时间

report 或者 check命令会增加脚本运行时间,为了减少运行时间,可以并行多核执行命令

1.在DCG mode下,可以使用命令redirect -bg指定后台运行的命令以及执行命令的cores。但是后台最多只能指定两个后台运行的任务,只有后台活跃任务少于两个,剩余的任务才能运行.支持 report analysis等命令

2.在redirect -bg命令使用时,需要关闭set_svf命令,等redirect -bg使用完成之后,才能继续使用。

parallel_execute用来并行执行命令,如果默认没有update_timing,则parallel_execute会自动执行update_timing

在综合中划分模块

综合中,模块划分可以减少综合时间,但是查的划分会增加block的尺寸,增加优化时间。

考虑设计重用划分

设计重用可以减少设计时间,根据设计重用的目的进行划分可以利用实例化设计减少设计时间

保存组合逻辑设计完整性

1.将相关的组合逻辑和它的目标寄存器组合在一起

2.消除glue logic(胶连逻辑), “Do not add glue-logic at the top level”的意思就是说在设计的顶层连接各个子模块的时候要直接相连,而不要插入一些简单逻辑来连接各个子模块。

以寄存器作为输出

为了简化约束定义,将寄存器作为全部模块的输出。对约束编写有两个好处:

1.一个独立模块的输入驱动能力总是和平均的输入驱动能力相等

2.前一个模块的输入延时,总是和Flip-Flop路径延时相等,这样的话不需要考虑只有组合逻辑的路径,也就能够更好的进行时序预算

根据设计目的划分

设计如果为了更好的面积优化以及 timing critical ,则可以根据设计目的进行划分,这样就可以对特定的模块采用针对性的约束指定优化策略

根据编译技术进行划分

当设计中出现高度结构化的设计和随机设计时,可以对不同的模块采用不同的编译策略

1.高度结构化电路设计:例如,错误检测电路,这种电路包含大量的OR tree ,更加适合结构化编译

2.random design : 在flatten design 中出现的设计策略

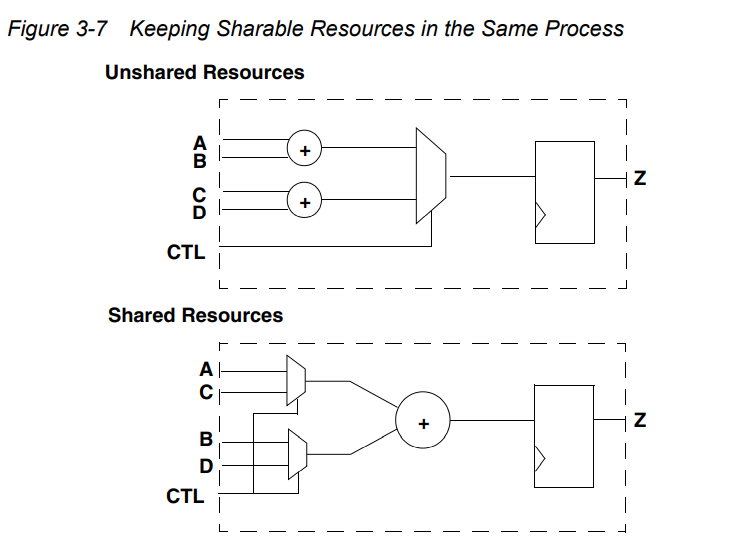

保证共享资源的一致性

资源共享只会出现在verilog中的always 语句块,DC 可以使用资源共享获取更好的设计质量,如下图所示:

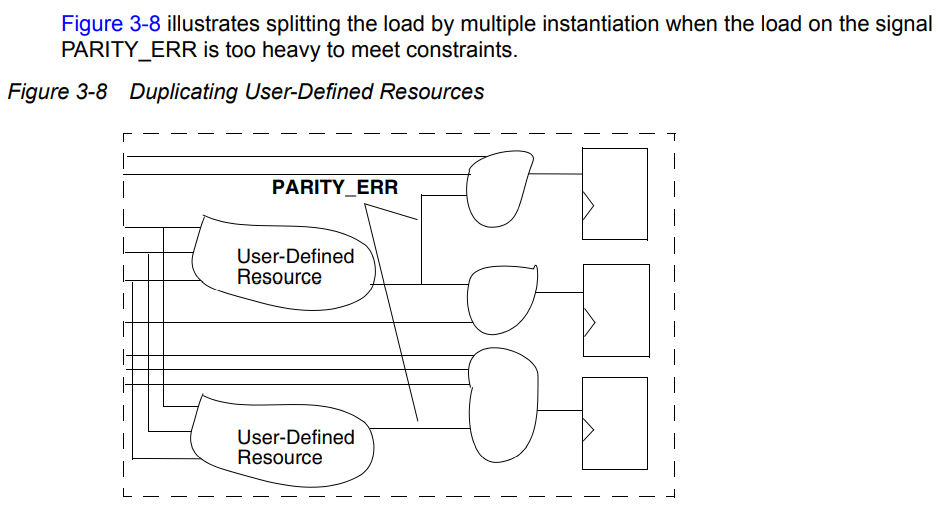

保证用户定义资源和驱动逻辑的完整性

user-defined resource是用户自定义的函数,程序或者是Macro cell,DC不会自动创建这些资源的实例化设计,当一个user-defined resource 实例化无法满足设计要求时,可以手动增加实例化设计的数目,来完成设计要求。

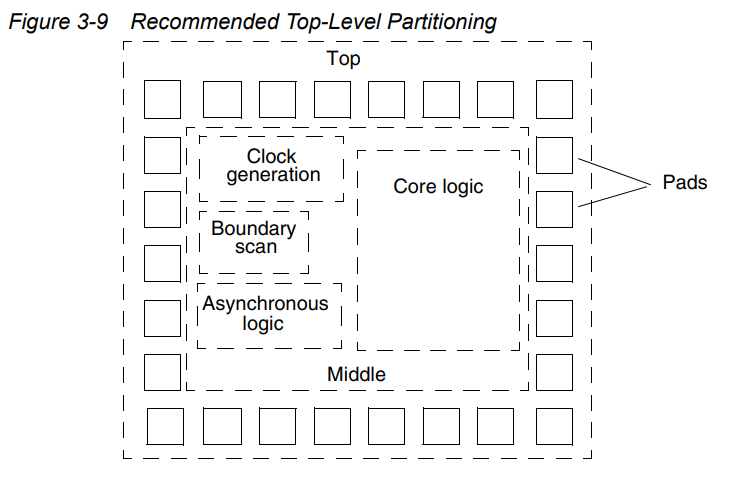

隔绝特定功能

可以通过功能在Top-level进行模块划分,例如隔离异步设计模块可以缩小STA问题分析的范围以及确定可测试性设计范围。

本博客所有文章除特别声明外,均采用 CC BY-SA 4.0 协议 ,转载请注明出处!